## Fabrication and Characterization of Ge Based Nano MOS Capacitor

## Rakesh Prasher<sup>1</sup>, Rakesh Vaid<sup>2</sup>

<sup>1</sup>Bharghva college of Engineering and Technology, Samba, India-184121 <sup>2</sup>Department of Physics and Electronics, University of Jammu, Jammu, India Email address: <sup>1</sup>prasher.rakesh@gmail.com, <sup>2</sup>rakeshvaid@ieee.org

Abstract—In the beginning of 21<sup>st</sup> century, many new electronic materials have been explored and incorporated into silicon CMOS transistors for enhancing their device performance and energy-efficiency. Beside silicon, germanium is another interesting candidate for nanoscale CMOS technology as it offers the mobility for electrons and holes exactly two and four times relative to Silicon. However, many issues still need to be addressed before Ge can be implemented in high-performance field-effect-transistor (FET) devices. One of the key issues is to provide a high-quality interfacial layer. In this paper various methods for Ge surface passivation (e.g. surface oxidation and nitridation), various high-k dielectrics materials, and deposition methods have been examined to attain proper interfacial properties. Further, fabrication and characterization of MOSCAP structures such as Al/HfO<sub>2</sub>/Ge has been presented. The deposition of HfO<sub>2</sub> on Ge substrate has been studied using atomic layer deposition (ALD) Different characterization techniques have been used to analyze these gate stack structures for the calculation of equivalent oxide thickness (EOT), dielectric constant (k), effective oxide charges/fixed oxide charges (Q<sub>eff</sub>) and interface trap density (D<sub>it</sub>). Ge MOS capacitors were successfully fabricated by depositing thin film of hafnia by ALD methods. The leakage current density, C–V hysteresis, charge trapping and interface state density can be significantly reduced by the surface nitridation of the Ge and also inhibits the formation of interfacial layer

Keywords—MOS capacitor; Surface passivation; Dielectric constant; EOT.

#### I. INTRODUCTION

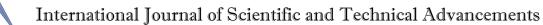

oday, the modern human society is becoming comfortable for high technology electronic products such as personal computer, mobile phones, video game machines, digital cameras, and human-like robots etc. by making use of ultra large scale integration (ULSI) technology. The silicon metal oxide semiconductor field effect transistor (MOSFET) has been the most essential building block of current ULSI integrated circuits (ICs) since its invention in the 1960s. The performance of silicon ULSI depends on the capability of the MOSFET, especially the processing speed and electrical power dissipation which are hanged on its geometrical size. The semiconductor industry has been loyally following Moore's law to regularly improve the performance and intricacies of ICs [1]. However, as silicon begins to reach its fundamental limits, even greater barriers need to be overcome where the use of more novel materials and device structures may be needed to continue CMOS scaling. Possessing extraordinary qualities such as low leakage current, low interface state density and good thermal stability, silicon (Si) has been used in MOS technology for many decades [2]. As per Moore's law, achieving high device density and faster switching speed will cause transistor gate length to shrink and reach around 7-5 nm by year 2020-2022. This results in dwindling of gate length and gate oxide thickness to 1 nm and ultimate oxide scaling down to EOT (Equivalent oxide thickness) of approximately 0.5 nm is required [3].

Recently, many new electronic materials have been explored and incorporated into silicon CMOS transistors. As this trend continues, it is expected that most of the non silicon materials will substitute silicon as the ultimate transistor channel material [4]. To review the physical limits,

microelectronics revolution has followed the non-silicon technology due to the possession of their excellent carrier transport properties, including carbon-based semiconductors such as carbon nanotubes [5], [6], graphene [7], [8], germanium (Ge) [9], [10] and III-V compound semiconductors [11], [12]. High mobility channel materials such as Ge and III-V compounds offer a potential solution to meet the power and performance specifications of future CMOS nodes. Beside silicon, germanium is an interesting candidate for nanoscale CMOS technology as it offers the mobility for electrons and holes exactly two and four times relative to Silicon. Reported room temperature hole mobility in a 7.5 nm thick Ge quantum well has exceeded 2500 cm<sup>2</sup>/V-sec [13]. High performance, n and p-channel Ge MOSFETs has been reported [14-19]. These alternate channel materials can enhance channel mobility beyond the physical limits of Si based MOS devices [20].

During the past years, many approaches have been examined to passivate the Ge surface. Surface nitridation of Ge was an early attempt, since GeOx was usually considered as a poor and unstable oxide. Epitaxial Si passivation of Ge surfaces has been well established and high performances were demonstrated for p-MOSFET devices. S passivation was effective for III-V compound semiconductors and was also investigated for Ge. Recently, GeO<sub>2</sub> interfacial layer (IL) exhibit promising properties as well. We will review those passivation methods and summarize the results from the existing literature. Many high-k oxides have comprehensively studied as a possible replacement for conventional SiO<sub>2</sub> such as Al<sub>2</sub>O<sub>3</sub> [21-22], HfO<sub>2</sub> [23], TiO<sub>2</sub> [24], CeO<sub>2</sub> [25], LaAlO<sub>3</sub> [26], HfSiO [27], ZrO<sub>2</sub> [28]. The deposition of a high-k dielectric can be achieved by various methods, including physical vapor deposition (PVD), molecular beam deposition (MBD) [29], chemical vapor

deposition (CVD), and atomic layer deposition (ALD) (thermal and plasma). Among these techniques, ALD received great interest due to its intrinsic self terminated growth nature. ALD is a cyclic deposition process that consists of sequential self-limited surface adsorption and reaction. It provides precise thickness control at the atomic level, which makes it the dominant deposition technique for high-k dielectrics in current MOS devices.

Among these high-k materials,  $HfO_2$  has been identified as promising candidate to meet the scaling requirements because of its high dielectric constant (20-25), high band gap (5.8 eV), superior thermal stability with silicon, low density of interface states and good electrical reliability. In order to obtain good electrical properties, a thin EOT and a thermally stable oxide layer, the fabrication of high k/Ge gate stacks have been reported due to the higher mobility of Ge. It has been seen that the interface layer between high-k dielectric film and Ge is much thinner than that between Si and a high-k dielectric film.

Fig. 1. TEM images of MOSFET scaling over the years with technological advances labeled (Source: Intel corp, USA).

The formation of GeO<sub>2</sub> on Ge was the biggest hindrance during the past few years for the fabrication of CMOS devices. There is also the problem of diffusion of Ge into HfO2 which causes device instability, high interface state density Dit and mobility degradation. Thus, in order to suppress the intrinsic GeO behavior, the nitridation of GeO<sub>2</sub> (GeON) is required. In order to improve these parameters further, nitridation of GeO<sub>2</sub> i.e., GeON IL has been suggested for enhancing its electrical properties. In this work, high k HfO<sub>2</sub> films has been deposited on two different ILs (GeO2 and GeON) for Ge gate stacks by ALD with thickness of 9.77 nm. The thickness of film was evaluated by Spectroscopic Ellipsometer (SE) and Filmetrics Reflectometer whereas the states of the elements and chemical compositions of the films were studied by X-ray Photoelectron Spectroscopy (XPS). High-frequency Capacitance-Voltage (C-V), Conductance-Voltage (G-V) and Current-Voltage (I-V) measurements were used to obtain the electrical properties of the Al/HfO<sub>2</sub>/Ge MOS capacitor.

#### II. EXPERIMENTAL DETAILS AND FABRICATED STRUCTURE

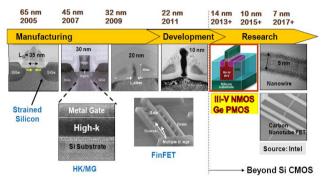

2" p-type Ge wafers having orientation <100> and 1-10  $\Omega\text{-cm}$  resistivity were used as substrates. Germanium dioxide (GeO $_2$ ) and germanium oxynitride (GeON) were used as surface passivation layers prior to the  $HfO_2$  dielectric

deposition. For surface nitridation, the initial oxide present on the Ge substrate was removed using a cyclic rinsing of acetone, IPA and de-ionized water followed by a rinse in 5:1 HF solution three times for 30 sec each and then blown dry in  $N_2$  gas. ANNEALSYS AS-ONE 150 RTP system was used for oxidation and nitridation of these samples for 3 minutes at 400°C in  $O_2$  and 600 °C in  $O_3$  ambient respectively. After the surface passivations, the Ge wafers were immediately transferred to a high vacuum ALD system (Nanotech Fiji 200) and deposition of  $O_3$  was performed at  $O_3$ 0°C using alternating surface-saturating reactions of  $O_3$ 1 HfCl<sub>4</sub> and  $O_3$ 2 Purging was done for 30 seconds after  $O_3$ 2 and 60 seconds for  $O_3$ 3 HfCl<sub>4</sub> pulse.

Fig. 2. Fabrication process flow for Al/HfO<sub>2</sub>/ILs/Ge p-MOS capacitor.

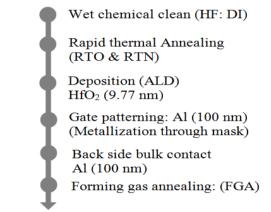

Fig. 3. Schematic of Al/Hf0 $_2$ /ILs/Ge p-MOS capacitor.

The thickness of HfO<sub>2</sub> was found to be about 9.77 nm as measured by an ellipsometer (SE 800) and filmetrics reflectometer. After that, a 1000 Å thick layer of aluminum (Al) was deposited using thermal evaporator-Al system through a shadow mask to pattern the capacitor electrode on the top hafnia layer to fabricate MOS capacitor structure for electrical properties measurements. Before the back contact formation, the buffered hydrofluoric acid (BHF) followed by three times rinsed in de-ionized water was used to remove the

native oxides. By thermally evaporating Al metal, an ohmic contact was formed on the backside of Ge substrate to form MOS capacitor. Finally, forming gas anneal (FGA) at 420 °C for 20 minutes using 96% N<sub>2</sub> and 4% H<sub>2</sub> ambient was performed with the fabricated Al/HfO<sub>2</sub>/ILs/Ge MOSCAP structure. X-Ray photoelectron spectroscopy (XPS) was used to analyze the states of the elements and chemical compositions. C-V, G-V and I-V measurements of fabricated MOS structures were performed to extract various electrical parameters using electrical characterization tool (VEGA). The complete process flow of Al/HfO<sub>2</sub>/ILs/Ge p-MOS capacitor fabrication is illustrated in fig. 2 and schematic of the Al/HfO<sub>2</sub>/ILs/Ge p-MOS capacitor is shown in fig. 3.

#### III. RESULTS AND DISCUSSION

In this paper, the effect of interfacial layers between  $HfO_2$  and Ge on the physical as well as electrical characteristics of Al/HfO<sub>2</sub>/ILs/Ge p-MOS capacitor has been discussed. We used oxidation for 3 minutes at 400°C in  $O_2$  ambient and nitridation for 3 minutes at 600 °C in  $NH_3$  ambient for surface passivation. Further the effect of forming gas annealing has also been discussed.

#### Thickness of HfO<sub>2</sub> Layer

The thickness of the  $HfO_2$  film was found to be 9.77 nm measured using variable angle spectroscopic ellipsometry and also by the filmetrics Reflectometer for the confirmation of the exact value. The thickness was calculated by taking the mean of all the values from both the methods. The refractive index for the deposited films was found to be in the range 2.12 - 2.42. The equivalent oxide thickness (EOT) with GeON as IL has been found to be 3.23 nm while with  $GeO_2$  as IL, the value of EOT found was 3.67 nm. These EOT values were determined using physical thickness of  $HfO_2$  layer and dielectric constant calculated from the capacitance voltage (CV) measurements.

#### X - Ray Spectroscopy

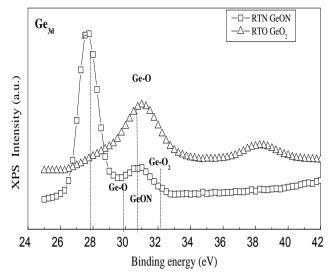

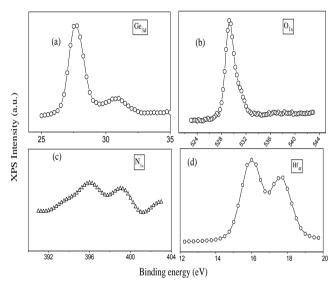

In fig. 5, the sample presents two Ge3d peaks at 28eV and 31eV and Ge3d XPS spectrum obtained from GeO2 grown at 400°C displays the presence of bonded oxygen in the state (sub-peak with 3.2 eV shift in binding energy from Ge3d peak) which confirmed the growth of GeO2 as the initial dielectric. The shifting of sub-peak towards the lower binding energy shows the presence of nitrogen atoms due to the nitridation of GeO2 and changes in its chemical state converting it into GeON. Fig. 5 shows the XPS depth profile of 9.77 nm thick HfO<sub>2</sub> diectric material on Ge substrate. In Fig 4 (d), when sample was scanned from the top, it displays two peaks at 16 eV and 17.7 eV which correspond to Hf4f peaks. On increasing the sputter depth, Ge3d region shows the presence of Ge-O, GeO2 and GeON peaks from the Ge substrate and confirmed the existence of Oxygen and Nitrogen atoms in the HfO2/Ge interlayer. O1s peak was detected at 529.25 eV as shown in figure 5 (b) and two peaks of N1s at 396.25 eV and 399.5 eV were also detected as shown in figure 5 (c) from the sample of HfO<sub>2</sub>/GeON/Ge stack. These peaks

suggest the formation of germinate of hafnium (HfGeO<sub>2</sub>/HfGeON).

Fig. 4. XPS spectra of Ge3d for GeO<sub>2</sub> and GeON.

Fig. 5. (a) Ge3d (b) O1s (c) N1s and Hf4f XPS depth profile of 9.77 nm  $HfO_2$  dielectric on Ge substrate.

Effect of Interfacial Layers (ILs) on Electrical Characteristics

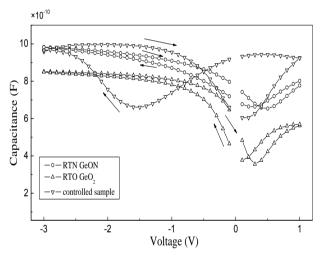

The normalized capacitance–voltage (C-V) curves for Al/HfO<sub>2</sub>/Ge p-MOS MOS capacitors for different interfacial layers at a frequency of 100 KHz were measured to verify the dielectric behavior of HfO<sub>2</sub> films. C-V characteristics of the devices with as ALD-deposited 9.77 nm HfO<sub>2</sub> film and GeO<sub>2</sub>/GeON ILs between HfO<sub>2</sub> and Ge substrate demonstrate typical MOS capacitor behavior. Comparison of C–V characteristics of MOSCAPs with Al/HfO<sub>2</sub>/Ge stack for two interfacial layers (ILs) with controlled sample is shown in fig. 6. As shown in this figure, the dc gate bias voltage was swept from a negative voltage to a positive voltage and then returned to the initial value (-3V to 1V). There occurs a positive shift for the flat band voltage with the increase in the annealing

temperature. Both interfacial layered HfO<sub>2</sub>/Ge stack shows better curves than controlled sample because of the improvement of interfacial trap density by the interfacial layer. For HfO<sub>2</sub>/GeON IL/Ge stack, a reduction in hysteresis window is seen as the traps have experienced an effective suppression. In accumulation region of C-V curve, the accumulation capacitance is observed to be increased the HfO<sub>2</sub>/RTN GeON IL/Ge stack because of the improvement of interfacial trap density (Dit) of the interfacial layer. Leakage is clearly visible in accumulation region in case of controlled sample which means as deposited HfO2 layer is due to trap charges. The value of dielectric constant (k) of the HfO<sub>2</sub> was extracted from the accumulation region of C-V curve in fig. 5. The calculated value of dielectric constant for HfO<sub>2</sub>/RTN GeON IL sample is fund to be 13. The lower dielectric constant may be due to presence of trap charges in the film that decides the quality of the film. In this Figure, flat band voltage V<sub>fb</sub> shifted toward the negative voltage has been observed for interfacial layers stack and was due to the existence of the positive effective oxide charge (Q<sub>eff</sub>) in the GeO<sub>2</sub>/GeON ILs and HfO<sub>2</sub>. Calculated value of Q<sub>eff</sub> in our work for three different samples of RTN GeON, RTO GeO2 ILs and controlled sample are  $16.92 \times 10^{12}$  cm<sup>-2</sup>,  $17.55 \times 10^{12}$  cm<sup>-</sup>  $^{2}$ , 11.5×10 $^{11}$  cm $^{-2}$ .

Fig. 6. Caparison of C-V characterstics for RTN GeON and RTO  $GeO_2$  ILs with controlled sample measured on Al/HfO<sub>2</sub>/Ge p-MOS capacitor at 100 KHz frequency.

The effect of interfacial layers on interface trap density ( $D_{\rm it}$ ) & effective oxide charges ( $Q_{\rm eff}$ ) has been listed in table 1. The value of  $D_{\rm it}$  of the  $HfO_2$  was extracted from the accumulation region of C-V curve in fig. 6 and inversion region of G-V curve. The calculated values are  $19.282\times10^{13}, 2.53\times10^{13}$  and  $0.63\times10^{12}~eV^{-1}~cm^{-2}$  for controlled (HfO<sub>2</sub>/Ge), HfO<sub>2</sub>/GeO<sub>2</sub>/Ge & HfO<sub>2</sub>/GeON/Ge samples respectively. It has been observed that a lower  $D_{\rm it}$  and less EOT were achieved for HfO<sub>2</sub>/GeON/Ge sample, which helps in the improvement of leakage current of the device. It clearly shows that HfO<sub>2</sub>/GeON/Ge sample leads to significant reduction in the  $D_{\rm it}$  at the expense of a slight increase in  $Q_{\rm eff}$ . The computed values of hysteresis from capacitance–voltage characteristics for each

sample are given in table 1. This significant shift in C–V hysteresis for GeON and GeO $_2$  ILs samples as compared to controlled sample indicates the improvement in dielectric layer, reduction in equivalent oxide thickness (EOT), reduction in interface trap density ( $D_{it}$ ), reduction in fixed oxide charges or effective oxide charges ( $Q_{eff}$ ). These properties decide the quality of the MOS capacitor. From this table it is concluded that the Al/HfO $_2$ /Ge p-MOS capacitor with very small C–V hysteresis and low gate leakage has been achieved with GeON interfacial layer.

Table 1. Key properties of different gate stack for Al/HfO<sub>2</sub>/Ge p-MOS Capacitor.

| Dielectric properties             | Controlled sample       | RTO<br>GeO <sub>2</sub> /HfO <sub>2</sub> | RTN<br>GeON/HfO <sub>2</sub> |

|-----------------------------------|-------------------------|-------------------------------------------|------------------------------|

| $D_{it} (eV^{-1} cm^{-2})$        | 1.928 ×10 <sup>14</sup> | $2.53 \times 10^{13}$                     | 6.3×10 <sup>11</sup>         |

| Thermal stability                 | Stable                  | Unstable                                  | Stable                       |

| Dielectric constant               | 11.6                    | 11.4                                      | 13                           |

| $Q_{\rm eff}$ (cm <sup>-2</sup> ) | $1.15 \times 10^{12}$   | $1.75 \times 10^{13}$                     | $1.69 \times 10^{13}$        |

| EOT (nm)                          | 3.27                    | 3.67                                      | 3.23                         |

#### IV. CONCLUSION

Thin film of hafnia with thickness of 9.77 nm was successfully deposited on n-type Ge substrate by ALD method. Physical and electrical characterization of the  $HfO_2$  thin film MOS capacitor with FGA at 420 °C temperature has been studied. Thickness of hafnia is determined by ellipsometer and profilometer. This study suggested that before deposition of  $HfO_2$  on Ge, surface must be mandatory which help us in improvement of overall nano device performance.

#### ACKNOWLEDGMENT

The authors acknowledge the CEN, IIT Bombay under INUP scheme which have been sponsored by DIT, MCIT, and Government of India for funding and providing us the facilities of fabrication and characterizations.

#### REFERENCES

- [1] G. E. Moore, "Cramming more components onto integrated circuits," Electronics, vol. 38, pp. 114, 1965.

- [2] R. Garg, D. Misra, and P. Swain, "Ge MOS capacitors with thermally evaporated HfO<sub>2</sub> as gate dielectric," *Journal of the Electrochemical Society*, vol. 153, pp. F29-F34, 2006.

- [3] A. G. Khairnar and A. M. Mahajan, "Effect of post-deposition annealing temperature on RF-sputtered HfO<sub>2</sub> thin film for advanced CMOS technology," *Solid State Sciences*, vol. 15, pp. 24-28, 2013.

- [4] J. E. Lilienfeld, U.S. Patent, pp. 1745175, 1930.

- [5] A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, "Logic circuits with carbon nanotube transistors," *Science*, vol. 294, pp. 1317-1320, 2001.

- [6] A. Javey, et al. "High-k dielectrics for advanced carbon-nanotube transistors and logic gates," *Nature materials*, vol. 1, pp. 241-246, 2002.

- [7] Y. Lin, C. Dimitrakopoulos, K. Jenkins, D. Farmer, H. Chium, A. Grill, and P. Avouris, "100-GHz transistors from wafer-scale epitaxial grapheme," *Science*, vol. 327, pp. 662, 2010.

- [8] F. Schwierz, "Graphene transistors," *Nature Nanotechnology*, vol. 5, pp. 487-496, 2010.

- [9] R. Pillarisetty, et al., "High mobility strained germanium quantum well field effect transistor as the p-channel device option for low power (Vcc = 0.5V) III-V CMOS architecture," *Proc. IEEE IEDM*, 2010.

# LIOTA

### International Journal of Scientific and Technical Advancements

ISSN: 2454-1532

- [10] W. Chern, P. Hashemi, J. Teherani, T. Yu, Y. Dong, G. Xia, D. Antoniadis, and J. Hoyt, "High-mobility high-k-all-around asymmetrically strained germanium nanowire trigate p-MOSFETs," Proc. IEEE IEDM. 2012.

- [11] J. Gu, Y. Liu, Y. Wu, R. Colby, R. Gordon, and P. Ye, "First experimental demonstration of gate-all-around III-V MOSFETs by topdown approach," *Proc. IEEE IEDM*, 2011.

- [12] M. Radosvaljevic, et al., "Electrostatics improvement in 3-D tri-gate over ultrathin body planer InGaAs quantum well field effect transistors with high-k gate dielectric and scaled gate-to-drain/gate-to-source separation," Proc. IEEE IEDM, 2011.

- [13] M. Myronov et al., "Temperature dependence of transport properties of high mobility holes in Ge quantum wells," *Journal of Applied Physics*, vol. 97, pp. 6, 2005.

- [14] M. Lee et al., Strained Ge channel p-type metal-oxide-semiconductor field-effect transistors grown on Si<sub>1-x</sub>Ge<sub>x</sub>/Si virtual substrates," *Applied Physics Letters*, vol. 79, pp. 3344-3346, 2001.

- [15] H. Shang et al., "High mobility p-Channel germanium MOSFETs with a thin Ge oxynitride gate dielectric," *IEEE IEDM*, pp. 441-444, 2002.

- [16] H. Shang et al., "Electrical characterization of germanium p-channel MOSFETs," *IEEE Electron Device Letters*, vol. 24, pp. 242-244, 2003.

- [17] C. Chui and K. Saraswat, "Advanced germanium MOSFET technologies with high-k gate dielectrics and shallow junctions," *International Conference on Integrated Circuit Design and Technology*, pp. 245-252, 2004

- [18] C. Chui, F. Ito, and K. Saraswat, "Scalability and electrical properties of germanium oxynitride MOS dielectrics," *IEEE Electron Device Letters*, vol. 25, pp. 613–615, 2004.

- [19] A. Nayfeh, C. Chui, T. Yonehara, and K. C. Saraswat, "Fabrication of high-quality p-MOSFET in Ge grown heteroepitaxially on Si", IEEE Electron Device Letters, vol. 26, pp. 311–313, 2005.

- [20] S. Chandra, M. Jeong, Y. Park, J. Yoon, and C. Choi, "Effect of annealing ambient on structural and electrical properties of Ge metal-

- oxide-semiconductor capacitors with Pt gate electrode and HfO2 gate dielectric," *Materials Transactions*, vol. 52, pp. 118-123, 2011.

- [21] J. Son, S. Jeong, K. Kim, and Y. Roh, "Electrical characterizations of HfO<sub>2</sub>/A<sub>2</sub>O<sub>3</sub>/Si as alternative gate dielectrics," *Journal of the Korean Physical Society*, vol. 51, pp. 238-240, 2007.

- [22] Y. Lui, W. Lan, Z. He, and Y. Wang, "Electrical properties of La-doped Al<sub>2</sub>O<sub>3</sub> films on Si (100) substrates as a high-dielectric-constant gate material," *Chinease Physics Letters*, vol. 23, pp. 2236-2238, 2006.

- [23] J. C. Hackley, T. Gougousi, "Properties of atomic layer deposited HfO<sub>2</sub> thin films", Thin Solid Films, vol. 517, pp. 6576-6583, 2009.

- [24] M. Kadoshima, M. Hiratani, Y. Shimamoto, S. Kimura, et.al, "Rutile-type TiO<sub>2</sub> thin film for high-k gate insulator," *Thin Solid Films*, vol. 424, pp. 224-228, 2003.

- [25] S. Chuah, K. Cheong, Z. Lockman, and Z. Hassan, "Effect of post-deposition annealing temperature on CeO<sub>2</sub> thin film deposited on silicon substrate via RF magnetron sputtering technique," *Materials Science in Semiconductor Processing*, vol. 14, pp. 101-107, 2011.

- [26] R. Kato, S. Kyogoku, M. Sakashita, H. Kondo, and S. Zaima, "Atomic layer deposition-Al<sub>2</sub>O<sub>3</sub> interface layers on interfacial properties of Ge metal—oxide—semiconductor capacitors," *Japanese Journal of Applied Physics*, vol. 48, pp. 05DA04, 2009.

- [27] Y. Oniki, Y. Iwazaki, M. Hasumi, T. Ueno, and K. Kuroiwa, "HfO<sub>2</sub>/Si and HfSiO/Si structures fabricated by oxidation of metal thin films," *Japanese Journal of Applied Physics*, vol. 48, pp. 05DA01, 2009.

- [28] Y. Keunbin, P. Yeonkyu, P. Anna, C. Namhee, L. Chongmu, "Electrical properties of sputter-deposited ZrO<sub>2</sub>-based Pt/ZrO<sub>2</sub>/Si capacitors," *Journal of Materials Science and Technology*, vol. 22, pp. 807-810, 2006.

- [29] M. Caymax, S. Elshocht, M. Houssa, A. Delabie, T. Conard, M. Meuris, et al., "sSOI fabrication by wafer bonding and layer splitting of thin SiGe virtual substrates," *Material Science Engeneering: B*, vol. 135, pp. 256–260, 2006.