# Novel Superjunction Power MOSFET

### Deepti Sharma<sup>1</sup>, Rakesh Vaid<sup>2</sup>

<sup>1, 2</sup>Department of Physics & Electronics, University of Jammu, J&K, India-180006 Email address: <sup>1</sup>deepti.sharma309@gmail.com, <sup>2</sup>rakeshvaid@ieee.org

**Abstract**—The present paper proposes a novel Superjunction (SJ) Power MOSFET. The reduction in the vertical electric field along the direction of current flow is observed with the use of buried oxide in the N-pillar of a conventional SJMOSFET using 2D device simulator. It is also seen that the relation between  $R_{on}$  and  $B_{v}$  is improved in proposed SJMOSFET. Further, the use of buried oxide leads to an enhancement of breakdown voltage  $(B_{v})$  by approx. 20% and reduction in the on-resistance  $(R_{on})$  by approx. 25%. The process flow of the proposed device is based on modifying the existing fabrication of super junction power MOSFET in which buried oxide (BOX) is created by using SIMOX (separation-by-implanted oxygen) process.

*Keywords*— Breakdown voltage (B<sub>v</sub>); on-resistance (R<sub>on</sub>); SJMOSFET; buried oxide (BOX).

#### I. Introduction

Power MOSFETs are ideally suited for use in many electronic applications. In the conventional power MOSFETs, a trade-off exists between specific onstate resistance  $(R_{on})$  and breakdown voltage  $(B_v)$  known as "silicon limit"  $[R_{on} \propto B_v^{2.5}]$  [1] that can be improved with a Superjunction (SJ) structure with n and p-pillars in the drift region which employed the charge compensation concept. Many SJMOSFET configurations have been studied to reduce the on-resistance and address the tradeoff between  $B_v$  and  $R_{on}$  such as Super junction devices (SJ), COOLMOS<sup>TM</sup> transistors, oxide filled extended trench gate super junction MOSFET structure etc [2-10].

In the present paper, an improved SJMOSFET is proposed, in which the concept of buried-oxide [11] has been used to further enhance the  $B_{\nu}$  and reduce the  $R_{on}$  to have a better relationship between  $R_{on}$  and  $B_{\nu}$ . The breakdown voltage has been increased in proposed SJMOSFET leading to an improvement in various other performance parameters e.g. current flow lines, potential etc.

#### II. DEVICE STRUCTURE

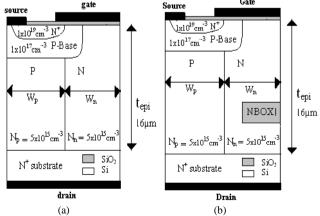

The typical structures of (a) conventional SJMOSFET and (b) proposed SJMOSFET with buried oxide (BOX) are shown in fig.1.

Fig. 1. Cros-sectional view of (a) Conventional (b) Proposed SJMOSFET with BOX

#### III. SIMULATION RESULTS AND DISCUSSION

In this section, we have compared the performance of conventional and proposed SJMOSFET in terms of electron concentration, current flow lines, electric field, breakdown voltage, on-resistance and current-voltage characteristics are obtained using the 2D device simulator PISCES.

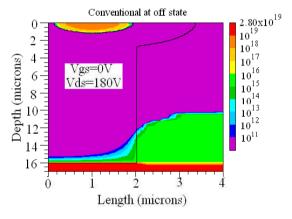

Fig. 2. 2-D Cross-sectional view of electron concentration of (a) conventional SJ-MOSFET (b) Proposed SJMOSFET.

The electron concentration of both the conventional and proposed SJMOSFET shown in fig. 2 in the off state suggests that the proposed SJMOSFET is more depleted of the charge carriers at higher  $V_{\rm ds}$  and the current path is blocked by the

BOX similar to the SOI–RESURF effect [12]. In the off state, the electron concentration is very less in the channel region since there is no conduction taking place under this condition. Further, it can be seen that electron concentration is maximum in the N-pillar due to the fact that current flow is taking place via this region only. The similar behavior of current flowlines is observed in on-state of both the conventional and proposed SJMOSFET.

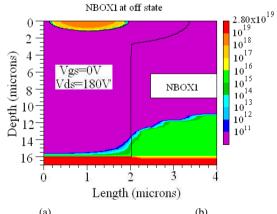

The electric field variation of the conventional and proposed SJMOSFET is illustrated in fig.3. It is seen that the vertical electric field along the direction of the current flow reduces in the off state in case of proposed SJMOSFET. The obvious reason for this reduction in electric field is the addition of BOX in the N-pillar of SJMOSFET as compared to the conventional SJMOSFET.

Fig. 3. Magnitude of electric field of the conventional and proposed SJMOSFET along the direction of current flow near the junction i.e. at  $2.2\mu m$  at Vds=180V.

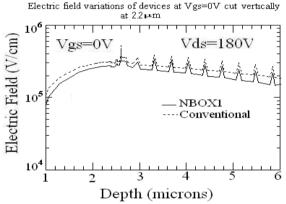

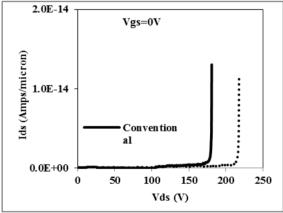

Fig. 4. Comparison of breakdown performance at  $V_{gs} = 0V$ .

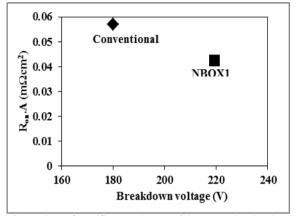

A comparison of the breakdown voltage and on-resistance of the conventional and proposed SJMOSFET is shown in fig. 4. The observed breakdown voltages ( $B_{\nu}$ ) of conventional and proposed SJMOSFET are 180 and 219 V respectively. A ~20% enhancement of breakdown voltage occurs in case of proposed SJMOSFET due to the addition of BOX in the N-pillar. Similarly, the specific on-resistance ( $R_{on}$ -A) of the conventional and proposed SJMOSFET achieved is 0.0569 m $\Omega$ cm<sup>2</sup> and 0.0425 m $\Omega$ cm<sup>2</sup> respectively. A 25% reduction of

$R_{on}$ . A occurs in the proposed SJMOSFET as compared to conventional SJMOSFET shown in fig.5.

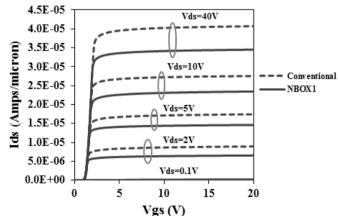

The current-voltage characteristics of the conventional and proposed SJMOSFET for various drain-sources voltages (Vds) is shown in fig. 6. It is seen in figure that the drain current of both the devices are increased with the increase in drain-source voltage. Further, it has been observed that the current conduction is reduced in case of proposed SJMOSFET due to the reduced conduction path which has been blocked by BOX.

Fig. 5. Comparison of specific on-resistance of the conventional and proposed SJMOSFET at Vds=0.1V.

Fig. 6.  $I_{ds}$ - $V_{gs}$  characteristics of the conventional and proposed SJMOSFET.

#### IV. CONCLUSION

In this paper, an improved structure of superjunction with buried oxide in the N-pillar of drift region is proposed and compared with the performance of conventional SJMOSFET. It can be concluded that with the implementation of BOX in the SJMOSFTET, the electron current and electric field shows excellent improvement. Further, we concluded that the breakdown voltage and on-resistance relationship is improved in proposed SJMOSFET which currently replace the conventional SJMOSFET and may use in various future applications.

#### REFERENCES

[1] G. Deboy, N. Marz, J. P. Stengl, H. Strack, J. Tihanyi, and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon," *in Proceedings IED M Tech. Dig.*, pp. 683, 1998.

### International Journal of Scientific and Technical Advancements

ISSN: 2454-1532

- [2] T. Fujihira, "Theory of semiconductor superjunction devices," *The Japan Society of Applied Physics*, vol. 36, pp. 6254-6262, 1997.

- [3] L. Lorenz, G. Deboy, A. Knapp, and M. Marz, "COOLMOS<sup>TM</sup>-a new milestone in high voltage power MOS," in *Proceedings IEEE ISPSD*, 1999, pp. 3.

- [4] B. J. Daniel, C. D. Parikh, and M. B. Patil, "Modeling of the CoolMOS<sup>TM</sup> transistor - Part I: Device physics," *IEEE Transactions on Electron Devices*, vol. 49, pp. 916-922, 2002.

- [5] P. N. Kondekar, "Analytical modeling and simulation studies of high voltage super-junction drift layer for power MOSFET," in Proceedings ICM, pp. 495, 2010.

- [6] W. C. Lin and S. Jun, "An oxide filled extended trench gate super junction MOSFET structure," *Chinese Physics B*, vol. 18, pp. 1231-1236, 2009.

- [7] W. Sun, J. Zhu, Q. Qian, P. Cao, S. Liu, Z. Su, L. Shengli, and S. Longxing, "Trench superjunction VDMOS with charge imbalance cells," *Solid-State Electronics*, vol. 64, pp. 14-17, 2011.

- [8] D. Sharma and R. Vaid, "Effect of drift region doping and column thickness variations in a super junction power MOSFET: a 2-D Simulation Study," *Journal of Nano- and Electronic Physics*, vol. 3, pp.1112-1117, 2011.

- [9] J. C. Hernandez, L. P. Petersen, M. A. E. Andersen, and N. H. Petersen, "Ultrafast switching superjunction MOSFETs for single phase PFC applications," in Proceedings IEEE APEC, pp. 143, 2014.

[10] Z. Lin, H. Huang, and X. B. Chen, "An improved superjunction

- [10] Z. Lin, H. Huang, and X. B. Chen, "An improved superjunction structure with variation vertical doping profile," *IEEE Transactions on Electron Devices*, vol. 62, pp. 228-231, 2015.

- [11] A. W. Ludikhuize, "A review of RESURF technology," in Proceeding 12th International Symposium on Power Semiconductor Devices & ICs, pp.11, 2000.

- [12] M. Kanechika, M. Kodama, T. Uesugi, and H. Tadano, "A concept of SOI RESURF lateral devices with striped trench electrodes," *IEEE Transactions on Electron devices*, vol. 52, pp. 1205-1210, 2005

## International Journal of Scientific and Technical Advancements

ISSN: 2454-1532