ISSN: 2454-1532

# Fabrication and Characterization of Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>~4.5nm/n-Si Nanoscale Device for Advanced CMOS Applications

Richa Gupta<sup>1</sup>, Renu<sup>2</sup>, Rakesh Vaid<sup>3</sup>

<sup>1, 2, 3</sup> Department of Physics and Electronics, University of Jammu, Jammu, India-180006 Email address: <sup>1</sup>richagupta@gmail.com, <sup>2</sup>rakeshvaid@ieee.org

Abstract—Downscaling is one of the attractive features supporting the technology node of present era. Ensuring the current status of ITRS, we reported the fabrication of nano-scale device based on high-k dielectric  $HfO_2$ . To examine the interfacial and structural properties of the grown films, various diagnostic techniques including Ellipsometry measurements, Atomic force microscopy (AFM), Field Emission Scanning Electron Microscopy (FESEM) and Fourier Transform Spectroscopy (FT-IR) were taken into account. Investigation of the electrical behavior of thin films directly corresponds to Capacitance-Voltage (C-V), Conductance-Voltage (G-V) and Current density versus Voltage (J-V) measurements. The fabricated nano-MOS offered the improved performance in terms of its reduced equivalent oxide thickness (EOT~3.87), leakage current density ( $J = 6.5 \times 10^{-8} \text{ A/cm}^2$  at  $V_g = 1\text{ V}$ ) and Interface trap density ( $D_{it} = 0.436 \times 10^{13} \text{ eV}^{-1}\text{cm}^{-2}$ ). Smaller EOT combined with the smaller leakage current can unlock the doors of power saving for nano-scale devices.

**Keywords**— High-k dielectrics; ALD; MOScap; interfacial layer; FTIR; D<sub>it</sub>; EOT.

#### I. INTRODUCTION

S the thickness of SiO<sub>2</sub> gate dielectric films used in CMOS devices is shrinked below 1.5 nm, the Lagate leakage current level becomes quite objectionable [1-3]. Extensive efforts have been made for finding the alternative gate dielectrics to triumph over the problem of leakage current [4-6]. Insulating materials with large dielectric constants (named as high-k materials) are alluring the modern industry owing to their potential use as gate dielectrics in metal-oxide semiconductor field-effect transistor (MOSFETs) [7-11]. Leakage current of gate oxides can be suppressed by the introduction of high-k dielectric to real applications [12-14]. A number of high-k dielectrics that have been dynamically pursued to replace SiO2. Among them are cerium oxide CeO<sub>2</sub> [15], gadolinium oxide Gd<sub>2</sub>O<sub>3</sub> [16], neodymium oxide Nd<sub>2</sub>O<sub>3</sub> [17], aluminum oxide Al<sub>2</sub>O<sub>3</sub> [18], lanthanum aluminum oxide LaAlO<sub>3</sub> [19], tantalum pentoxide Ta<sub>2</sub>O<sub>5</sub> [20], titanium dioxide TiO<sub>2</sub> [21], zirconium dioxide ZrO<sub>2</sub> [22], HfO<sub>2</sub>-CexHf1-xO<sub>2</sub> [23], hafnium silicate HfSixOy [24], and rare-earth scandates GdScO<sub>3</sub> [25], and SmScO<sub>3</sub> [26]. High-k materials hold the promise of achieving very high capacitance densities with relatively thicker films. However, finding a suitable high-k material is a major challenge. It appears that, after investigating a whole host of materials, Hafnium based gate dielectrics have emerged as the "ultimate" choice for high-k materials. The ideal motivation for moving to high-k gate dielectric was the need to trim down direct tunneling leakage currents [27]. Direct deposition of HfO<sub>2</sub> on Si substrate induces defects [28] due to biased amorphicity and residual contamination. This defect leads to high breakdown fields and avoids reduction of FET channel mobility [29]. A number of concerns are related with high-k dielectrics, which includes Coulomb scattering from bulk oxide charges, surface roughness scattering, interface fixed

charges, dielectric charge trapping and remote phonon scattering associated with reliability problems. A peep into the past research reveals following issues to be taken into consideration:

- Influence of manufacturable ex situ and in situ high-k dielectrics

- Conventional process routes and materials such as HfO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub> to form quality gate stacks

- Engineering the high-k channel interface by valuation of bi-layer schemes to attain low Dit and thin EOT.

- Development of various schemes or models for passivating these defects.

We have worked on several issues related to direct deposition of  $HfO_2$  on Si substrate. The problems arised has been resolved by incorporating good quality  $SiO_2$  as an interfacial layer.

#### II. EXPERIMENTAL DETAILS

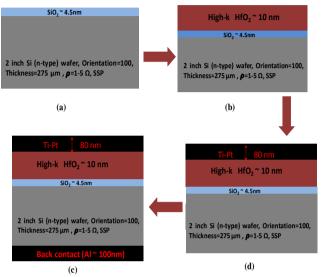

The fabricated double layer nano-MOS is shown in Figure 1. Single side polished (SSP) n-type Si <100> substrates having a resistivity of 1-5  $\Omega$  cm were chemically cleaned by the standard RCA method. SiO<sub>2</sub> ~ 4.5nm was grown using RTP at 900 <sup>0</sup>C having 900 sccm O<sub>2</sub> flow per minute under atmospheric conditions. Atomic layer deposition (ALD) technique was used to deposit 10nm thin hafnia film on silicon dioxide at 200°C by thermal method. The physical thickness of SiO<sub>2</sub> and HfO<sub>2</sub> films were determined by using SE800 Ellipsometer. For the top gate electrode, 1000°A thick layer with Ti = 20nm and Pt = 60nm was deposited by 4 target Ebeam evaporator system over a circular area of  $2.2 \times 10^{-4}$  cm<sup>2</sup> through a shadow mask. To remove the native oxide on the back side, etching was performed by buffered hydrofluoric acid (BHF) followed by rinsing in de-ionized water. On the back side of silicon wafer, Aluminum film was deposited for

making back contact. Finally, Post metallization annealing (PMA) was performed at 420 °C for 20 minutes using forming gas (96%  $N_2$ , 4%  $H_2$ ) ambient. To extract the various performance parameters, the measurements of the fabricated device were carried out using Keithley 4200-SCS at room temperature under dark conditions. The process flow of the fabricated device can be clearly illustrated as:

Fig. 1. Process flow for fabricated nano-scale device (a)  $SiO_2$  interfacial layer growth (b) ALD  $HfO_2 \sim 10$ nm (c) Ti-Pt front gate deposition and (d) Al as a back contact

#### III. AFM STUDY

Using AFM, it is quite viable to evaluate the roughness of a sample surface at a high resolution. Moreover, this method distinguishes the sample based on its mechanical properties such as - hardness and roughness.

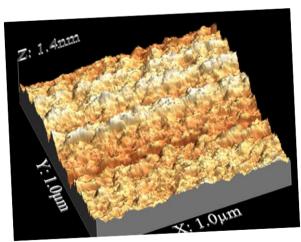

Fig. 2. 3-D AFM image of SiO<sub>2</sub> having  $2 \times 2 \mu m$  scanning area.

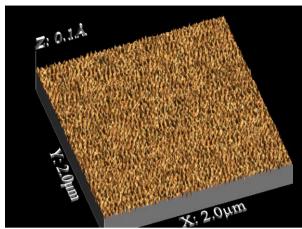

Figure 2 and 3 represents the atomic force measurement of silicon dioxide and hafnia films respectively. The surface roughness for  $SiO_2$  film was found to be 0.1838nm while the hafnia film prepared by atomic layer deposition technique indicates the rms value of 0.007295 nm.

Fig. 3. 3-D AFM image of HfO<sub>2</sub> having 2 × 2 μm scanning area.

The reduced roughness of SiO<sub>2</sub> film was the result of effective rapid thermal processing. In principle, the morphology of hafnia film exhibited the excellent film quality.

#### IV. ELLIPSOMETRY MEASUREMENTS

Ellipsometry works on the principle of interaction of light with the sample which produces a change in the intensity/polarization of the measuring beam. The change contains the information on sample which is measured. In this letter, we have used the Cauchy model for thickness and refractive index measurements. Cauchy method reflects the relationship existing between refractive index ' $\eta$ ' and wavelength ' $\lambda$ ' of a light for a transparent material. The measured parameters from this method can be represented by Table 1 as:

Table 1. Measured parameters by Cauchy method.

|                         | 700                      |

|-------------------------|--------------------------|

| Air                     | $\eta_{\mathrm{Air}}$    |

| Cauchy HfO <sub>2</sub> | 2.21                     |

| Cauchy SiO <sub>2</sub> | 1.45                     |

|                         | $\eta = 3.66, K = 0.027$ |

Here, the incident angle was kept as  $70^{\circ}$ C and computed extinction coefficient 'K' was 0.027. The respective measured thickness of SiO<sub>2</sub> and HfO<sub>2</sub> was 4.5nm and 10nm while their refractive indexes were found to be 2.21 and 1.45 respectively.

#### V. FESEM ANALYSIS

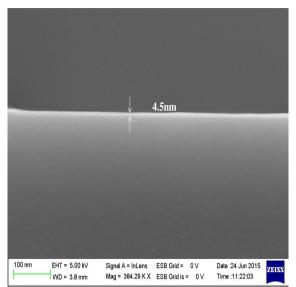

Figure 4 represents the field emission scanning electron microscopy analysis to corroborate the thickness of the interfacial layer. By using this physical characterization, we are certain to display the thickness of the grown  $SiO_2$  film  $\sim$  4.5nm. Prior to the growth of interfacial layer, standard RCA

cleaning process was performed to remove the native oxides and impurities.

Fig. 4. FESEM image of SiO<sub>2</sub> interfacial layer (Cross-sectional view).

The cross-sectional FESEM analysis reveals the formation of defect-free interfacial layer growth.

#### VI. FT-IR CHARACTERIZATION

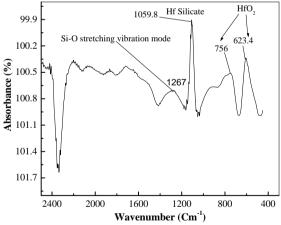

Figure 5 represents the FT-IR spectra of the hafnia film. The bonding structure was investigated by finding oxygen content in the film. To reflect the absorbance of the grown film, infrared absorption spectra of the bare-Silicon wafer was used as background spectra and finally subtracted from the total spectrum.

Fig. 5. FT-IR analysis of ALD Hafnia film.

The sharp vibration bands observed in the range of 623-756 cm<sup>-1</sup> validates the presence of HfO<sub>2</sub> (Frank, et al. 2004). The peak at 1059 cm<sup>-1</sup> corresponds to the shifting peak position of Hf-O towards the higher wave number series, and is somewhat following the crystalline category.

#### VII. RESULTS AND DISCUSSION

In this section, we shall deal with the electrical characterization namely C-V, G-V and I-V of the fabricated device structure.

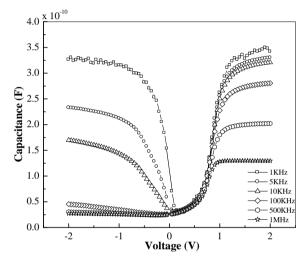

#### A. Capacitance Versus Voltage (C-V)

Figure 6 shows the Capacitance-voltage characteristics of Ti-Pt/HfO $_2$ /SiO $_2$ /Si MOS capacitor. C-V curve measurements were performed for frequency variation from 1 KHz and 1 MHz. However, all the calculations were carried out at high-frequency 500 KHz. The dielectric constant (K) of the device was calculated to be 14.6 as extracted from the accumulation region of C-V curve and the Equation (1) was used for its computation as:

Fig. 6. C-V characterization of Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/n-Si of nano-scale MOS.

$$K = \frac{(C_{ox}t_{ox})}{\epsilon_0 A} \tag{1}$$

where,  $C_{ox}$  = oxide capacitance,  $t_{ox}$  = oxide thickness,  $\epsilon_{0}$  = permittivity of the free space and 'A' represents the electrode area.

The effective oxide charge ( $Q_{\text{eff}}$ ) was calculated using Equation (2) as:

$$Q_{\text{eff}} = (\Delta V_{\text{fb}} \times C_{\text{ox}}) / (q \times A)$$

(2)

where,  $\Delta V_{fb}\!=\!$  flat band voltage shift,  $C_{ox}\!=\!$  Oxide Capacitance and 'q' denotes the electronic charge.

The value of  $Q_{eff}$  for 500 KHz was found to be  $0.4545 \times 10^{15}~cm^{-2}$ . A sufficient positive shift occurred in the flat-band voltage because of the existence of negative trap charges in the fabricated p-MOS structure.

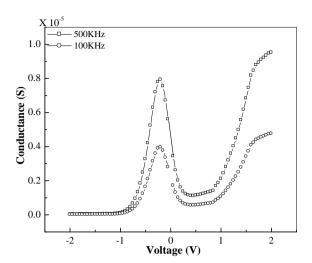

#### B. Conductance Versus Voltage (G-V)

Figure 7 shows G-V characteristics of the Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/n-Si stack studied at a frequency of 100 KHz and 500 KHz. The measurements demonstrate that there is an increase in the conductance value i.e.  $G_{max}$  at 500 KHz near the flat band voltage regime.

Fig. 7. G-V characterization of Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/n-Si of nano-scale MOS.

The interface trap density (D<sub>it</sub>) at interface was calculated from the Conductance Voltage characteristics by the following formula [8].

$$D_{it} = \frac{2\omega C_{ox}^{2} G_{max}}{qA[G_{max}^{2} + \omega^{2} (C_{ox} - C_{m} G_{max})^{2}]}$$

(3)

where,  $C_m$  is maximum capacitance,  $G_{max}$  is the maximum conductance and  $\omega$  is frequency. The obtained  $D_{it}$  value for the fabricated capacitor was found to be  $0.436 \times 10^{13} \ eV^{-1} \ cm^{-2}$  as per the above given relation. The reduction in the interface trap density  $D_{it}$  is the outcome of improved dangling bonds at the interface.

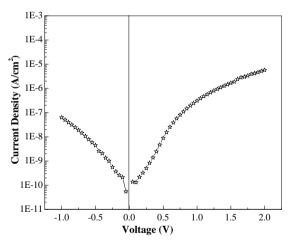

Fig. 8. J-V curve of Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/n-Si MOS capacitor.

#### C. Current Density Versus Voltage (J-V)

The leakage current density (J) of Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>/n-Si stack was measured as a function of voltage as represented by Figure 8. The leakage current density was observed to be improved up to  $6.5 \times 10^{-8}$  A/cm<sup>2</sup> after the incorporation of good quality interfacial layer of SiO<sub>2</sub> owing to the reduction of defects at the interface of Si/HfO<sub>2</sub> stack. Consequently, the significant decline in the device leakage was the result of

injection of charge carriers into the conduction band of hafnia film by Fowler-Northeium (FN) tunneling. This leakage reduction accounts for the enhanced device performance.

#### VIII. CONCLUSIONS

We successfully fabricated Ti-Pt/HfO<sub>2</sub>/SiO<sub>2</sub>~4.5nm/n-Si nanoscale device with achieved K~14.6. AFM studies confirms that the smoothness of grown films. A remarkable decrease in the interface trap density was observed owing to the interface improvement of Si/SiO<sub>2</sub>/HfO<sub>2</sub> stack. Moreover, effective reduction in EOT was achieved. High-k deposition along with the ultra thin interfacial layer of SiO<sub>2</sub> will leads to further device scaling without adverse leakage effects. Such a progress in device scaling is the gateway to power saving.

#### ACKNOWLEDGMENTS

The authors acknowledge the Centre of Excellence in Nanotechnology (CEN) at IIT Bombay under INUP scheme sponsored by DIT, MCIT and Government of India for funding and providing us the excellent facilities of fabrication and characterization.

#### REFERENCES

- [1] P. C. Juan, C. H. Liu, C. L. Lin, S. C. JU, M. G. Chen, Y. K. Chang, and J. H. Lu, "Electrical characterization and dielectric property of MIS capacitors using a high-k CeZrO<sub>4</sub> ternary oxide as the gate dielectric," *Journal of Applied Physics*, vol. 48, pp. 1-5, 2009.

- [2] G. F. Dong and Y. Qiu, "Pentacene thin-film transistors with Ta<sub>2</sub>O<sub>5</sub> as the gate dielectric," *Journal of Korean Physical Society*, vol. 54, pp. 493-497, 2009.

- [3] X. H. Zhu, J. M. Zhu, A. D. Li, Z. G. Liu, and N. B. Ming, "Challenges in atomic-scale characterization of high-k dielectrics and metal gate electrodes for advanced CMOS gate stacks," *Journal of Material Science and Technology*, vol. 25, pp. 289–313, 2009.

- [4] M. Rahmani, M. T. Ahmadi, H. K. F. Abadi, M. Saeidmanesh, E. Akbari, and R. Ismail, "Analytical modeling of trilayer graphene nanoribbon Schottky-barrier FET for high-speed switching applications," *Nanoscale Research Letters*, vol. 8, pp. 1-13, 2013.

- [5] S. J. Ding, H. B. Chen, X. M. Cui, S. Chen, Q. Q. Sun, P. Zhou, H. L. Lu, D. W. Zhang, and C. Shen, "Atomic layer deposition of high-density Pt nanodots on Al<sub>2</sub>O<sub>3</sub> film using (MeCp)Pt(Me)<sub>3</sub> and O<sub>2</sub> precursors for nonvolatile memory applications," *Nanoscale Research Letters*, vol. 8, pp. 1-7, 2013.

- [6] P. R. Chalker, M. Werner, S. Romani, R. J. Potter, K. Black, H. C. Aspinall, A.C. Jones, C. Z. Zhao, S. Taylor, and P. N. Heys, "Permittivity enhancement of hafnium dioxide high-k films by cerium doping," *Applied Physics Letters*, vol. 93, pp. 182911-1 182911-3, 2008.

- [7] S. H. Chen, W. S. Liao, H. C. Yang, S. J. Wang, Y. G. Liaw, H. Wang, H. S. Gu, and M. C. Wang, "High-performance III-V MOSFET with nano-stacked high-k gate dielectric and 3D fin-shaped structure," *Nanoscale Research Letters*, vol.7, pp. 1-5, 2012.

- [8] J. C. Wang, C. T. Lin, and C. H. Chen, "Gadolinium oxide nanocrystal nonvolatile memory with HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> nanostructure tunneling layers," *Nanoscale Research Letters*, vol. 7, pp. 1-9, 2012.

- [9] L. Shi and Z. G. Liu, "Characterization upon electrical hysteresis and thermal diffusion of TiAl<sub>3</sub>O<sub>x</sub> dielectric film," *Nanoscale Research Letters*, vol. 6, 2011.

- [10] W. Banerjee and S. Maikap, "High-k Hf-based nanocrystal memory capacitor with IrOx metal gate for NAND application," *IEEE International Workshop on Memory Technology, Design, and Testing*, (MTDT), pp. 31-33, 2009.

- [11] F. H. Chen, J. L. Her, Y. H. Shao, Y. H. Matsuda, and T. M. Pan, "Structural and electrical characteristics of high-k Er<sub>2</sub>O<sub>3</sub> and Er<sub>2</sub>TiO<sub>5</sub> gate dielectrics for a-IGZO thin-film transistors," *Nanoscale Research Letters*, vol. 8, pp. 1-5, 2013.

### International Journal of Scientific and Technical Advancements

ISSN: 2454-1532

- [12] G. Dalapati, T. S. Wong, Y. Li, C. Chia, A. Das, C. Mahata, H. Gao, S. Chattopadhyay, M. Kumar, H. Seng, C. Maiti, and D. Chi, "Characterization of epitaxial GaAs MOS capacitors using atomic layer-deposited TiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stack: study of Ge auto-doping and p-type Zn doping," *Nanoscale Research Letters*, vol. 7, 2012.

- [13] Y. T. An, C. Labbé, L. Khomenkova, M. Morales, X. Portier, and F. Gourbilleau, "Microstructure and optical properties of Pr<sup>3+</sup>doped hafnium silicate films," *Nanoscale Research Letters*, vol. 8, 2013.

- [14] P. Zhou, L. Ye, Q. Q. Sun, P. F. Wang, A. Q. Jiang, S. J. Ding, and D. W. Zhang, "Effect of concurrent joule heat and charge trapping on RESET for NbAlO fabricated by atomic layer deposition," *Nanoscale Research Letters*, vol. 8, 2013.

- [15] P. J. King et al., "Effect of deposition temperature on the properties of CeO<sub>2</sub> films grown by atomic layer deposition," *Thin Solid Films*, vol 519, pp. 4192–4195, 2011.

- [16] J. Robertson and B. Falabretti, "Band offsets of high-k gate oxides on III-V semiconductors," *Journal of Applied Physics*, vol. 1, pp. 014111– 014111, 2006.

- [17] J. Anthony, H. C. Aspinall, P. R. Chalker, R. J. Potter, T. D. Manning, Y. F. Loo, R. O'Kane, J. M. Gaskell, and L. M. Smith, "MOCVD and ALD of high-k dielectric oxides using alkoxide precursors," *Chemical Vapour Deposition*, vol. 12, pp. 83-98, 2006.

- [18] G. Adamopoulos, S. Thomas, D. D. Bradley, M. A. McLachlan, and T. D. Anthopoulos, "Low-voltage ZnO thin-film transistors based on Y<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> high-k dielectrics deposited by spray pyrolysis in air," *Applied Physics Letters*, vol. 98, pp. 123503-1- 123503-3, 2011.

- [19] L. Yan, H. B. Lu, G. T. Tan, F. Chen, Y. L. Zhou, G. Z. Yang, W. Liu, and Z. H. Chen, "High quality, high-k gate dielectric: amorphous LaAlO<sub>3</sub> thin films grown on Si (100) without Si interfacial layer," *Applied Physica A*, vol. 5, pp. 721-724, 2003.

- [20] T. M. Pan, T. F. Lie, T. S. Chao, K. L. Chang, and K. C. Hsieh, "High quality ultrathin CoTiO<sub>3</sub> high-k gate dielectrics," *Electrochemical Solid-State Letters*, vol. 9, pp. 433-434, 2000.

- [21] S. K. Kim, K. M. Kim, O. S. Kwon, S. W. Lee, C. B. Jeon, W. Y. Park, C. S. Hwang, and J. Jeong, "Structurally and electrically uniform

- deposition of high-k TiO<sub>2</sub> thin films on a Ru electrode in threedimensional contact holes using atomic layer deposition," *Electrochemical Solid-State Letters*, vol. 12, pp. F59–F62, 2005.

- [22] G. Adamopoulos, S. Thomas, P. H. Wöbkenberg, D. D. Bradley, M. A. McLachlan, and T. D. Anthopoulos, "High-mobility low-voltage ZnO and Li-doped ZnO transistors based on ZrO<sub>2</sub> high-k dielectric grown by spray pyrolysis in ambient air," *Advanced Materials*, vol. 16, pp. 1894-1898, 2011.

- [23] H. Gang, B. Deng, Z. Q. Sun, X. S. Chen, Y. M. Liu, and L. D. Zhang, "CVD-derived Hf-based high-k gate dielectrics," *Critical Review Solid State Material Sciences*, vol. 4, pp. 235-261, 2013.

- [24] H. Watanabe, M. Saitoh, N. Ikarashi, and Tatsumi T, "High-quality HfSi<sub>x</sub>O<sub>y</sub> gate dielectrics fabricated by solid phase interface reaction between physical- vapor -deposited metal-Hf and SiO<sub>2</sub> underlayer," *Applied Physics Letters*, vol. 3, pp. 449-451, 2004.

- [25] P. Myllymäki, M. Roeckerath, M. Putkonen, S. Lenk, J. Schubert, L. Niinistö, and S. Mant, "Characterization and electrical properties of high-k GdScO<sub>3</sub> thin films grown by atomic layer deposition," *Applied Physics A*, vol. 4, pp. 633–637, 2007.

- [26] A. P. Milanov, K. Xu, S. Cwik, H. Parala, T. Arcos, H. W. Becker, and A. Devi, "Sc<sub>2</sub>O<sub>3</sub>, Er<sub>2</sub>O<sub>3</sub>, and Y<sub>2</sub>O<sub>3</sub> thin films by MOCVD from volatile guanidinate class of rare-earth precursors," *Dalton Transactions*, vol. 45, pp. 13936–13947, 2012.

- [27] L. Colombo, J. J. Chambers, and H. Niimi, "Gate dielectric process technology for the Sub-1 nm equivalent oxide thickness (EOT) era," *The Electrochemical Society Interface*, pp. 51-54, 2007.

- [28] V. Fiorentini and G. Gulleri, "Theoretical evaluation of zirconium and hafnia as gate oxides for Si microelectronics," *Physical Review Letters*, vol. 89, pp. 266101-266104, 2002.

- [29] V. Kaushik, M. Claes, A. Delabie, S. V. Elshocht, O. Richard, T. Conard, E. Rohr, T. Witters, M. Caymax, S. D. Gendt, M. Heyns, "Observation and characterization of defects in HfO<sub>2</sub> high-k gate dielectric layers," *Microelectronics Reliability*, vol. 45, pp. 798-801, 2005.

## International Journal of Scientific and Technical Advancements

ISSN: 2454-1532